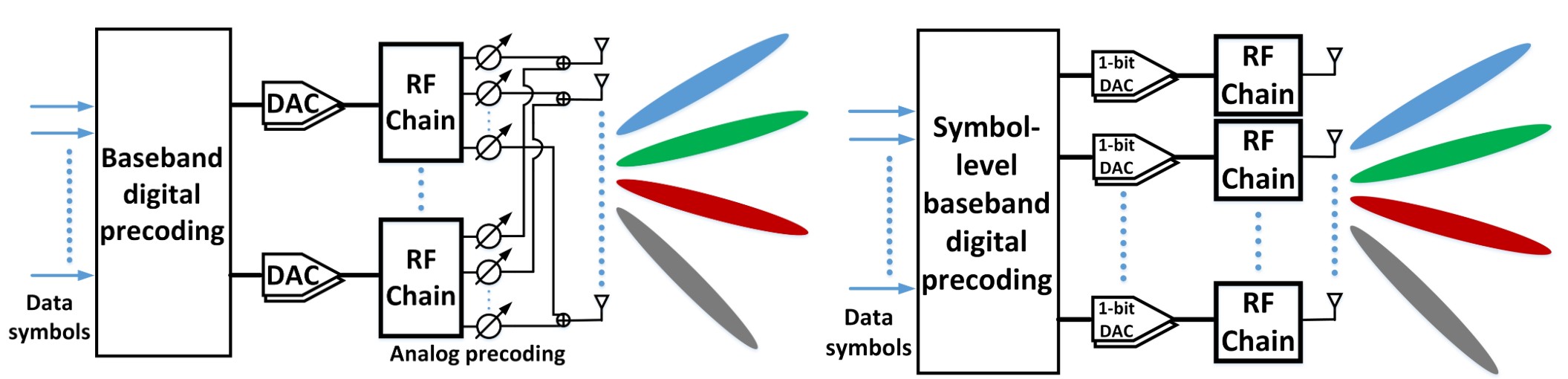

Another research focus of mine is hardware-efficient massive MIMO precoding. Massive multiple-input multiple-output (MIMO) has widely been acknowledged as a key enabling technology for the fifth-generation (5G) and future wireless communication systems. In the downlink transmission of a massive MIMO system, it has been shown that low-complexity linear precoding approaches such as zero-forcing (ZF) and regularized ZF (RZF) can achieve near-optimal performance. Nevertheless, the near optimality is achieved assuming that fully-digital processing and high-resolution digital-to-analog converters (DACs) are employed at the base station (BS). Such fully-digital processing requires a dedicated radio frequency (RF) chain and a pair of high-resolution DACs for each antenna element, which results in a significant increase in the hardware complexity and cost when the number of transmit antennas scales up. Moreover, the resulting power consumption of the large number of hardware components will also be prohibitive for practical implementation. All of the above drawbacks make fully-digital processing highly undesirable for a massive MIMO BS. Accordingly, there have been several emerging techniques that aim to reduce the hardware complexity and the power consumption for a massive MIMO BS, among which the hybrid analog-digital (AD) precoding and the use of low-resolution DACs are the most popular ones, as shown below.

Examples for hardware-efficient massive MIMO architectures

(Left) Hybrid Analog-Digital Architecture; (Right) Low-Resolution DACs Architecture